Intel ha finalmente svelato le caratteristiche chiave della nuova architettura SoC Alder Lake. In particolare sono stati presentati i nuovi core ad alta efficienza e quelli ad elevate prestazioni, insieme al Thread Director che gestirà il loro utilizzo in base alle esigenze dell'utente. Infine sono state discusse le caratteristiche chiave dei SoC Alder Lake, rappresentate dalla struttura dei SoC, il supporto alle più moderne memorie DDR5 e la compatibilità con le moderne interfacce PCIe di quinta generazione. Tutto questo è stato realizzato per offrire un elevato stacco rispetto al passato, garantito anche dal passaggio alla tecnologia a 10 nanometri SuperFin.

Andiamo dunque a scoprire nel dettaglio tutte le specifiche tecniche e le caratteristiche dell'architettura Intel Alder Lake per i nuovi SoC in arrivo nel 2021.

Cos’è Alder Lake?

L'arrivo di Alder Lake segna un notevole passo in avanti per Intel nell'architettura multi core x86. Finalmente il produttore statunitense ha abbandonato la tecnica costruttiva a 14 nanometri per passare a quella da 10 nanometri SuperFin. Inutile dire che questa transizione ha portato a numerosi vantaggi, creando un bel divario rispetto alle precedenti generazioni di SoC. Questa nuova architettura Alder Lake sarà la base delle prossime CPU Intel per il mercato desktop e mobile che arriveranno sul mercato entro la fine dell'anno.

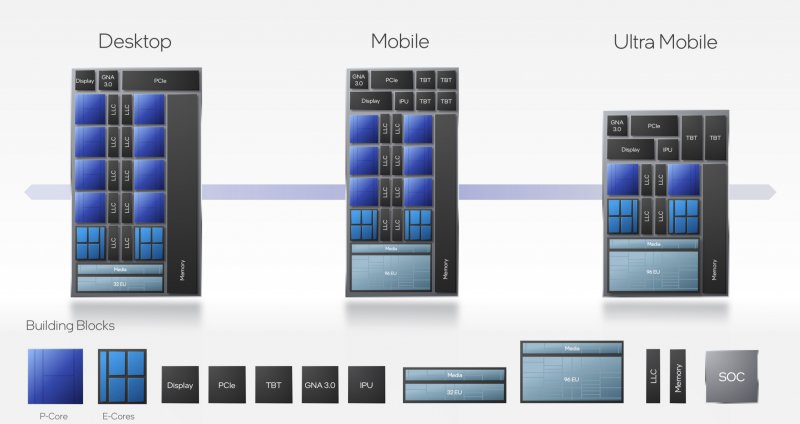

In fase di progettazione Intel ha fissato tre importanti obiettivi per Alder Lake con i quali effettuare questo importante passo in avanti. Il primo di questi è rappresentato dall'architettura SoC altamente scalabile, adatta sia ai dispositivi desktop che mobile e ultra mobile. Successivamente Intel ha progettato due nuovi core, uno ad alta efficienza ed un altro ad alte prestazioni. Per far lavorare simultaneamente le due tipologie di core è stato implementato direttamente nell'hardware il Thread Director. Infine, come terza importante novità di Alder Lake, Intel ha voluto portare il supporto avanzato alle più recenti tecnologie di memorie e I/O come la compatibilità con DDR5 e PCIe di quinta generazione.

Efficient-core

Il nuovo Efficient-core (E-core) di Intel rappresenta indubbiamente un elemento chiave della nuova architettura Alder Lake. Intel ha voluto progettare il core con architettura x86 più efficiente al mondo, tenendo in considerazione le prestazioni multithread scalabili per il multitasking moderno. Efficient-core funziona a bassa tensione per ridurre il consumo energetico complessivo, creando al contempo il margine di potenza per operare a frequenze più elevate. Intel ha potuto lavorare su una varietà di innovazioni tecniche per dare priorità ai carichi di lavoro, senza sprecare potenza di calcolo e incrementare le prestazioni con funzionalità che migliorano le istruzioni per ciclo. Tra le innovazioni degne di nota ci sono:

- 5.000 entry branch target cache per una più accurata branch prediction

- Cache di istruzioni da 64 kilobyte per mantenere vicine le istruzioni utili senza consumare la potenza del sottosistema di memoria

- Il primo decodificatore di lunghezza delle istruzioni on-demand di Intel che genera informazioni pre-decodifica

- Decodificatore out-of-order in cluster di Intel che consente di decodificare fino a sei istruzioni per ciclo mantenendo l'efficienza energetica

- Un ampio back-end con allocazione 5-wide e ritiro da 8-wide, 256 entry out-of-order window e 17 porte di esecuzione

- Robuste funzionalità di sicurezza che supportano la tecnologia Intel per l'applicazione del flusso di controllo e la protezione del reindirizzamento della tecnologia di virtualizzazione Intel

- L'implementazione di AVX ISA, insieme a nuove estensioni per supportare le operazioni integrali di intelligenza artificiale (AI)

Tutto questo si traduce in una performance complessiva migliorata rispetto alla CPU Skylake con il 40% in più di prestazioni a pari potenza oppure offre le stesse prestazioni consumando meno del 40% dell'energia. Per quanto riguarda invece le prestazioni di throughput, quattro core Efficient offrono l'80% in più di prestazioni pur consumando meno energia rispetto a due core Skylake che eseguono quattro thread o le stesse prestazioni di throughput consumando l'80% in meno di energia.

Performance-core

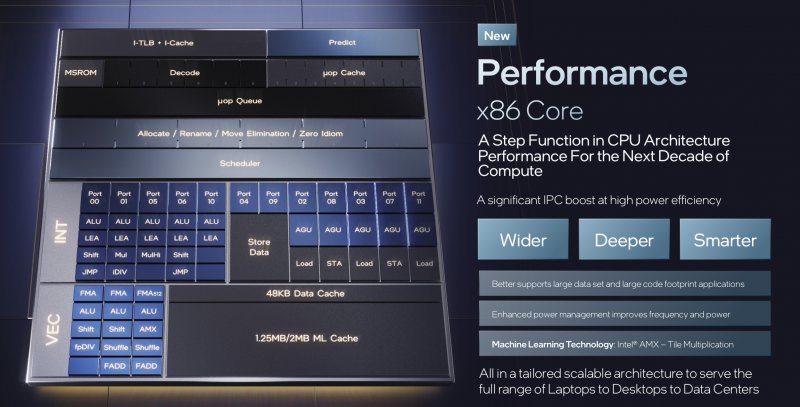

Con un Efficient-core di questo livello non poteva mancare ad un Performance-core (P-core) altrettanto innovativo. Intel ha voluto creare un core disegnato appositamente per la velocità e l'ulteriore riduzione della latenza, aumentando al contempo le prestazioni delle applicazioni a thread singolo. I carichi di lavoro sono sostenuti da codici sempre più complessi che richiedono maggiori capacità di esecuzione. Anche i dataset crescono enormemente insieme ai requisiti di ampiezza di banda dei dati. La nuova microarchitettura Performance-core di Intel offre un significativo aumento delle prestazioni per tutti gli usi e un migliore supporto per applicazioni sostenute da codice di grandi dimensioni. In particolare il produttore statunitense ha concentrato i propri sforzi su un allargato front-end, il quale va a prendere le istruzioni e le decodifica in micro-operazioni per metterle in coda ancora più grande. Successivamente l'Out of Order Engine (anch'esso allargato per massimizzare le performance) prende le micro-operazioni in coda e le spedisce alle unità esecutive. Quest'ultime sono state riviste con delle nuove ed ottimizzate Integer Execution Units e Vector Execution Units. L'ampliamento delle parti appena discusse ha portato ad un inevitabile allargamento delle L1 e L2 Cache ed un miglioramento prestazionale dell'intero Memory Subsystem. Performance core presenta un'architettura più ampia, profonda e intelligente:

- Più ampia: sei decoder (due in più); μop cache 8-wide (rispetto a sei); allocazione da sei (rispetto a cinque); 12 porte di esecuzione (rispetto a 10)

- Più profonda: file di registro più grandi; file di registro fisico più grandi; buffer di riordino più profondo con 512 voci

- Più intelligente: migliore accuratezza della branch prediction; latenza L1 effettiva ridotta; ottimizzazioni dell'ampiezza di banda predittiva di scrittura completa in L2

Complessivamente Intel ha raggiunto uno stacco di performance di circa 19% rispetto ai core di undicesima generazione a frequenza ISO per prestazioni generiche. Il P-core include inoltre Intel Advanced Matrix Extensions (AMX), l'acceleratore AI integrato di nuova generazione, progettato per il deep learning e maggiori prestazioni nelle istruzioni.

Thread Director

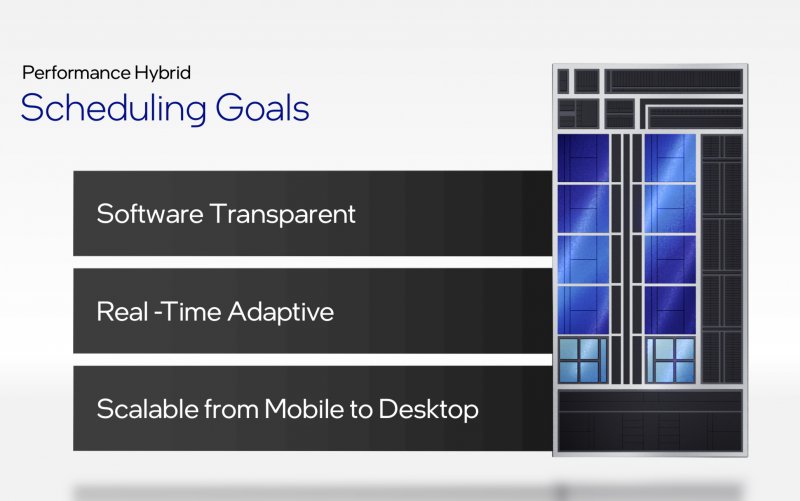

Una volta progettati i due nuovi core, Intel ha dovuto pensare ad una soluzione efficiente per farli lavorare insieme. Per questo motivo nasce Intel Thread Director, che suddivide il lavoro tra le due tipologie di core per massimizzare le prestazioni e l'efficienza della CPU. L'obiettivo che si sono posti in fase di progettazione era quello di trovare una soluzione dinamica in grado di adattarsi al software utilizzato dall'utente in tempo reale. Thread Director inoltre lavora in maniera completamente autonoma, senza la necessità degli sviluppatori di apportare delle modifiche al proprio software. Essendo una soluzione hardware integrata direttamente nei core è in grado di monitorare in tempo reale i programmi in esecuzione in ogni singolo thread. Inoltre, Thread Director invia un feedback continuo al sistema operativo per prendere delle decisioni ottimali sulla suddivisione dei processi nei core ad alta efficienza ed alte prestazioni, cosa che prima non poteva fare con questa trasparenza tra hardware e software. Allo stesso tempo Thread Director deve anche considerare le temperature dei singoli core e la potenza elettrica a disposizione per poter garantire un funzionamento ottimale in qualsiasi situazione. Tradizionalmente, il sistema operativo prendeva decisioni in base ai limitati dati statistici disponibili, ad esempio attività in primo piano e in background. Thread Director aggiunge una nuova dimensione di funzionamento per una maggiore ottimizzazione:

- Utilizzando la telemetria hardware per indirizzare i thread che richiedono prestazioni più elevate al giusto Performance-core in quel momento

- Monitorando mix di istruzioni, lo stato del core e di altri dati di telemetria relativi alla microarchitettura a livello capillare, che aiutano il sistema operativo a prendere decisioni di pianificazione più intelligenti

- Ottimizzando il Thread Director per le migliori prestazioni su Windows 11 grazie alla collaborazione con Microsoft

- Estendendo l'API PowerThrottling, che consente agli sviluppatori di specificare in modo esplicito attributi di qualità del servizio per i propri thread

- Applicando una nuova classificazione EcoQoS che informa lo scheduler se il thread preferisce l'efficienza energetica (tali thread vengono schedulati su Efficient-core)

Cerchiamo di capire meglio come lavora Intel Thread Director con un esempio di funzionamento. Quando l'utente avvia un software particolarmente impegnativo come un gioco o un programma di video editing, questo processo viene assegnato ad un core ad alte prestazioni (P-core). Altri programmi come il client mail che continuerà a sincronizzare la posta elettronica, verrà assegnato invece al core ad alta efficienza (E-core). Ipotizziamo che tutti i P-core siano impegnati a svolgere dei processi impegnativi, ma l'utente vorrebbe avviarne uno nuovo particolarmente pesante come un applicazione AI. In questo caso Thread Director è in grado di spostare il processo meno impegnativo dai P-core ai E-core, dando spazio al nuovo processo in arrivo. Tutto questo funziona in maniera dinamica. Se dopo qualche secondo l'applicazione AI non necessità più di un'elevata potenza di calcolo, verrà immediatamente spostata in un E-core. Lo stesso accade ad esempio con un videogioco messo in pausa, dove la necessità di potenza di calcolo è ridotta, quindi può passare ad un E-core per tornare al P-core non appena riprendiamo a giocare.

Specifiche tecniche

Passiamo infine alle specifiche tecniche di Alder Lake, dando dapprima un'occhiata alla struttura dei SoC. Intel ha previsto fino a 16 core per chip, con 8 P-core e 8 E-core, ognuno dotato di high dynamic frequency. Il numero massimo di thread invece raggiunge 24, con 2 thread per ogni P-core e 1 thread per ogni E-core. Infine il SoC Alder Lake avrà fino a 30 MB di LL Cache. Ovviamente il numero di P-core e E-core dipenderà dalla tipologia di dispositivo sul quale andranno montati i nuovi SoC Alder Lake. Ad esempio sui dispositivi desktop troveremo 8 P-core, mentre sugli ultra mobile solamente 2 P-core. Sfruttando un'unica architettura SoC, Intel vuole creare tre diversi chip:

- Un desktop con socket a due chip con prestazioni elevate, efficienza energetica, memoria e I/O

- Un pacchetto BGA mobile ad alte prestazioni che aggiunge immagini, grafica Xe più grande e connettività Thunderbolt 4

- Un packaging sottile, a basso consumo e alta densità con I/O e alimentazione ottimizzati

Intel con Alder Lake garantisce la compatibilità con le più moderne tecnologie di memorie. In particolar modo Alder Lake è compatibile con DDR5-4800, DDR4-3200, LP5-5200 e LP4x-4266 utilizzando il Dynamic voltage-frequency scaling ed abilitando l'overcloking avanzato. Intel vuole dunque abbracciare la transizione alle memorie DDR5, offrendo una compatibilità pressoché totale con tutte le tecnologie per dare massima libertà all'utente finale.

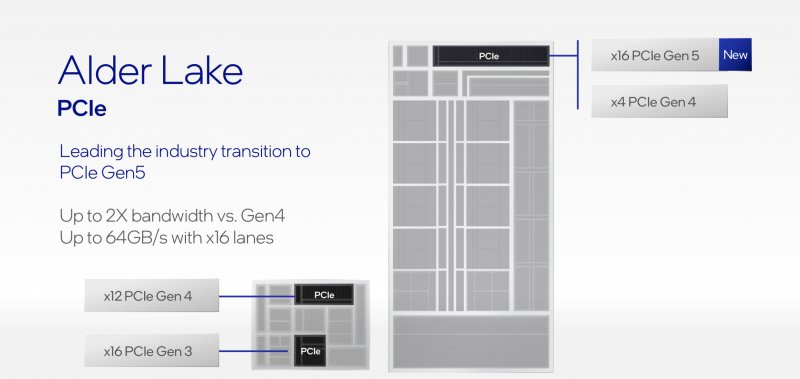

Anche sul fronte della connettività PCIe Alder Lake è assolutamente all'avanguardia. La nuova architettura Intel supporta infatti il nuovo standard PCIe di quinta generazione, il quale offre una banda passante fino a due volte superiore rispetto alla Gen4 ed una velocità di trasferimento fino a 64 GB/s con un connettore x16. Il supporto PCIe di Alder Lake si estende da x16 PCIe Gen5, x4 PCIe Gen4, x12 PCIe Gen4 fino ad arrivare a x16 PCIe Gen3. Non manca nemmeno il supporto a Thunderbolt 4 e Wi-Fi 6E. La complessità di costruire un'architettura così altamente scalabile consiste nel soddisfare le incredibili richieste di ampiezza di banda degli agenti di elaborazione e I/O senza compromettere la potenza. Per far lavorare tutti i core, le memorie e le interfacce PCIe alla massima velocità riducendo al minimo la latenza, Intel ha progettato tre fabric indipendenti:

- La fabric di calcolo può supportare fino a 1.000 gigabyte al secondo (GBps), ovvero 100 GBps per core o per cluster e collega i core e la grafica alla memoria tramite la cache di ultimo livello. Presenta inoltre un'elevata gamma di frequenza dinamica ed è in grado di selezionare dinamicamente il percorso dei dati per la latenza rispetto all'ottimizzazione della larghezza di banda in base ai carichi di fabric effettivi. Regola dinamicamente anche la politica della cache di ultimo livello, inclusiva o non inclusiva, in base all'utilizzo

- La fabric I/O supporta fino a 64 GBps, collegando i diversi tipi di I/O e dispositivi interni e può cambiare velocità senza interruzioni senza interferire con il normale funzionamento di un dispositivo, selezionando la velocità della fabric in modo che corrisponda alla quantità richiesta di trasferimento dati

- La fabric di memoria può fornire fino a 204 GBps di dati e ridimensionare dinamicamente la larghezza e la velocità del bus per supportare più punti operativi per ampiezza di banda elevata, bassa latenza o basso consumo