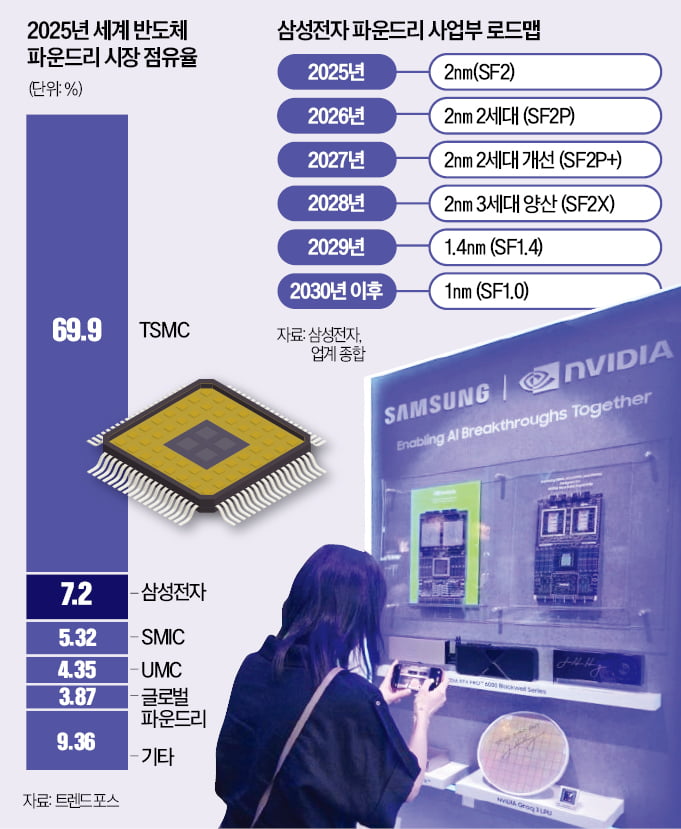

Samsung starebbe già guardando oltre il nodo a 2 nanometri per i suoi chip. Secondo nuove indiscrezioni, l'azienda starebbe lavorando al processo a 1 nm, spesso definito "dream semiconductor" per il livello di miniaturizzazione che promette di raggiungere.

I tempi, però, non sono immediati. Le attività di ricerca e sviluppo dovrebbero concludersi intorno al 2030, mentre l'introduzione in produzione è indicata per il 2031. Ridurre ulteriormente le dimensioni rispetto ai 2 nm rappresenta una sfida complessa, sia dal punto di vista tecnologico sia industriale.

Le sfide del processo produttivo a 1 nm: la struttura fork sheet

Per affrontarla, Samsung starebbe valutando l'adozione di una struttura chiamata fork sheet. Questa soluzione prevede l'inserimento di una barriera isolante tra i transistor, con l'obiettivo di aumentare la densità senza ampliare la superficie del chip. In pratica, si tratta di ottimizzare lo spazio disponibile, inserendo più componenti nello stesso ingombro.

La tecnologia attuale a 2 nm si basa sull'architettura GAA, acronimo di Gate-All-Around, che migliora l'efficienza energetica aumentando il controllo del flusso di corrente. Tuttavia, secondo le fonti, questo approccio potrebbe non essere sufficiente per il passaggio al nodo successivo, rendendo necessario un cambiamento strutturale.

L'idea alla base del fork sheet può essere paragonata a una diversa gestione degli spazi in ambito edilizio: invece di lasciare aree vuote tra gli elementi, queste vengono occupate per incrementare la densità complessiva. Il risultato atteso è un numero maggiore di transistor per unità di superficie, con potenziali benefici in termini di prestazioni.

Il percorso verso i nodi più avanzati non è però privo di ostacoli. In passato, Samsung avrebbe valutato anche un processo a 1,4 nm, successivamente rinviato per concentrare le risorse sullo sviluppo del 2 nm GAA. Le difficoltà produttive potrebbero aver influenzato queste scelte, spingendo l'azienda a rivedere le priorità.

Restano inoltre alcune criticità legate all'efficienza energetica. I primi risultati emersi su chip recenti indicano consumi elevati in determinate condizioni, un aspetto che incide direttamente sull'autonomia dei dispositivi. Questo suggerisce che il lavoro sul nodo a 2 nm non sia ancora completo sotto il profilo dell'ottimizzazione.

Il progetto a 1 nm si inserisce quindi in una strategia più ampia, che richiede progressi intermedi prima di arrivare alla maturità industriale. Nei prossimi anni sarà fondamentale verificare se le soluzioni proposte riusciranno a tradursi in vantaggi concreti, soprattutto in termini di efficienza e affidabilità produttiva.

Per conoscere i dettagli della nostra policy editoriale, è disponibile la pagina etica.