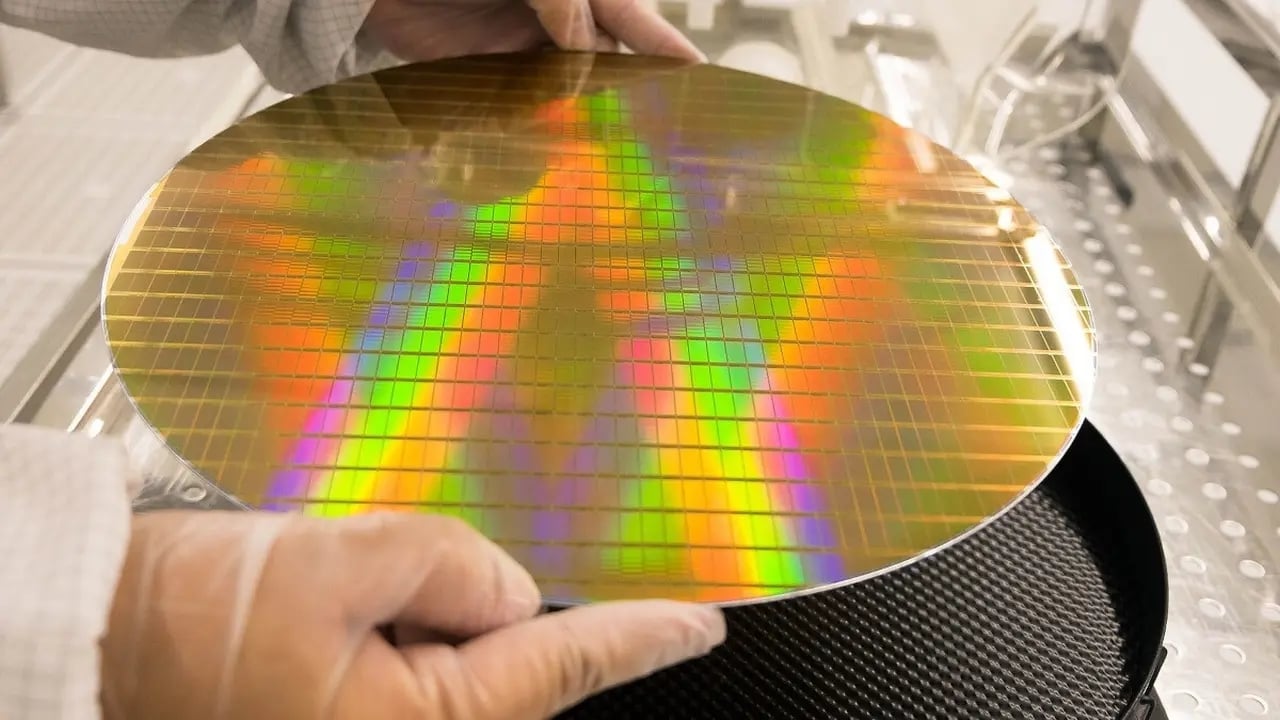

L'ascesa dell'intelligenza artificiale e la domanda crescente di chip avanzati stanno mettendo sotto pressione l'intera industria dei semiconduttori, ma nessuno quanto TSMC. L'azienda taiwanese, leader mondiale nella produzione di wafer, si trova oggi a gestire un livello di richieste tale da portare quasi al limite la propria capacità produttiva per i chip a 3 nanometri.

Clienti come NVIDIA, Apple, Qualcomm e MediaTek stanno prenotando volumi sempre più consistenti, al punto che gli analisti prevedono un pieno utilizzo degli impianti entro il prossimo anno. Nonostante i tentativi di riorganizzare le linee di produzione e ottimizzare i flussi, il rischio di un deficit produttivo resta concreto. La corsa ai chip più efficienti e potenti non mostra segni di rallentamento, e TSMC deve ora affrontare un dilemma: espandere rapidamente la capacità o rivedere i costi per mantenere la redditività di fronte a una domanda che supera ogni previsione.

Prezzi più altri del 100% per i chip a 3nm?

Secondo quanto riportato dal Commercial Times e analizzato dagli esperti di JPMorgan, TSMC starebbe intervenendo su diverse linee produttive per rispondere alla pressione crescente dei principali committenti. L'obiettivo è ampliare la capacità di produzione dei wafer a 3 nanometri, attualmente la più richiesta del mercato. Alcune linee dedicate ai chip a 4nm saranno riconvertite per supportare la produzione a 3nm, con un incremento previsto di circa 25.000 wafer al mese. Parallelamente, gli impianti già predisposti per le future generazioni a 2 nanometri - i nodi N2 e A16 - continueranno a essere sviluppati, ma con un ritmo più graduale.

Le linee meno utilizzate dedicate ai processi a 6 e 7 nanometri saranno anch'esse impiegate per la fase di back-end dei 3nm, contribuendo con un output aggiuntivo di 5.000-10.000 wafer mensili. Si tratta di una strategia d'emergenza per far fronte a una domanda che, a questo ritmo, rischia di superare anche le capacità di un colosso come TSMC.

Le previsioni iniziali indicavano che la produzione mensile dei chip a 3nm avrebbe potuto raggiungere 160.000 wafer entro la fine del 2025, ma le nuove stime parlano di un traguardo più modesto: tra 140.000 e 145.000 wafer, e soltanto entro la fine del 2026. La differenza non è irrilevante, considerando che NVIDIA avrebbe già chiesto a TSMC di aumentare la capacità fino al livello originariamente previsto per poter soddisfare le proprie necessità legate al mercato delle GPU e dei data center per l'IA.

Paradossalmente, i limiti produttivi di TSMC stanno generando un vantaggio economico inatteso. JPMorgan riferisce che, per garantirsi consegne rapide, alcuni clienti avrebbero accettato di pagare "hot run prices", ovvero tariffe superiori dal 50 al 100 percento rispetto ai costi standard. Questi ordini rappresentano solo il 10 percento del totale, ma permettono all'azienda di mantenere margini lordi superiori al 60 percento, consolidando ulteriormente la propria posizione finanziaria.

Oltre agli aumenti straordinari per le commesse più urgenti, si prevede anche un rincaro generalizzato fino al 10 percento sui listini, una mossa inevitabile in un contesto dove la domanda supera di gran lunga l'offerta. La pressione esercitata dai grandi clienti non riguarda solo la disponibilità di chip, ma anche i tempi di consegna e la priorità nelle forniture, un aspetto che sta diventando cruciale nel settore tecnologico globale.

Nel frattempo, TSMC non può trascurare le prossime tappe del proprio sviluppo industriale. La produzione di massa dei chip a 2 nanometri è prevista per la fine del 2025, un traguardo che richiederà ingenti investimenti e una gestione accurata delle risorse. In più sono partiti i lavori per una fabbrica da record, che produrrà chip da 1,4 nm in soli 3 anni.

Per conoscere i dettagli della nostra policy editoriale, è disponibile la pagina etica.